# Modeling Total Ionizing Dose Effects in Deep Submicron CMOS Technologies

Michael McLain, Hugh Barnaby, Ivan Sanchez

School of Electrical, Computer and Energy Engineering Ira A. Fulton School of Engineering Arizona State University, Tempe, AZ

## **Acknowledgements**

#### We would like to thank AFOSR and the MURI program

We would also like to acknowledge the additional support of DTRA, DARPA, NASA, and the Boeing Corp.

### **Motivation**

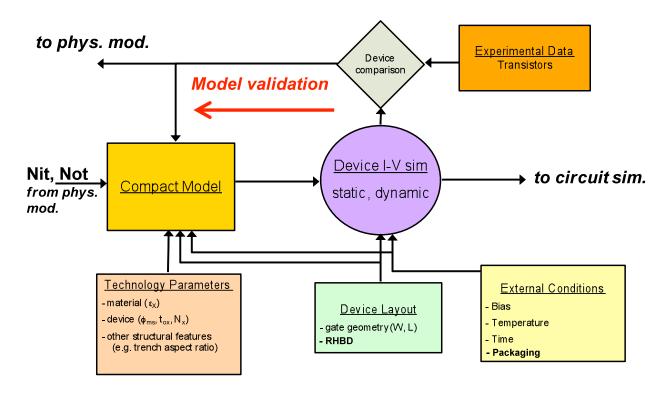

- Characterize and model radiation damage effects in modern CMOS device technologies

- Technologies:

- deep submicron bulk CMOS,

- silicon on insulator (El-Mamouni VU, Sanchez ASU)

MURI 2009

May 2005 - "Device-level Radiation Effects Modeling"

Overview of numerical (TCAD) simulation approaches to modeling radiation effects in CMOS devices

#### **Sheet Charge**

#### **Trapped Charge vol. distribution**

5

June 2006 - "Total Ionizing Dose Effects in Bulk Technologies and Devices"

Characterize, parameterize TID effects. Formalize closed form analytical expressions for TID effects in devices (130nm CMOS).

- June 2007 "Modeling Total Ionizing Dose Effects in Deep Submicron Bulk CMOS technologies"

- Description and initial validation of radiation-enabled compact modeling approach for CMOS technologies (≥ 90nm CMOS).

**MURI 2009**

- May 2008 Surface potential-based analytical modeling of TID effects in bulk CMOS devices

- Closed form analytical models used to estimate charge build-up in STI sidewall and fit degraded I-V characteristics in nFETs

# Recent Work (2009)

- Demonstration of analytical model of TID effects on bulk CMOS isolations oxides

- Revised analytical model for TID defect buildup compared to FOXFET I-V and TCAD simulations

- Demonstration of modeling approach: SRAM with reverse body bias

- Effects of Channel Implant Variation on Edge Leakage Currents

- Modeling TID effects in Multiple Gate FETs

**MURI 2009**

# Recent Work (2009)

- Demonstration of analytical model of TID effects on bulk CMOS isolations oxides

- Revised analytical model for TID defect buildup compared to FOXFET I-V and TCAD simulations

- Demonstration of modeling approach: SRAM with reverse body bias

- Effects of Channel Implant Variation on Edge Leakage Currents

- Modeling TID effects in Multiple Gate FETs

MURI 2009

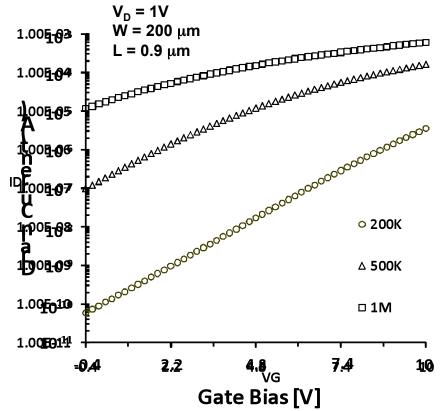

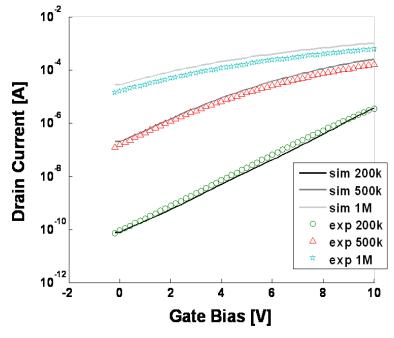

## **Field Oxide FET Measurements**

# TID experiments on FOXFETS used to calibrate the analytical model

- <sup>60</sup>Co irradiation source (DR ~ 20 rad/s)

- 90 nm LP technology

## **Defect Extraction**

#### Defect potential in SP equations used to fit FOXFET data

$$I_{Drift} = (V_{gb} - V_{fb})(\psi_{sd} - \psi_{ss}) - \frac{1}{2}(\psi_{sd}^2 - \psi_{ss}^2)$$

$$-2\frac{\gamma}{3}\Big[(\psi_{sd} - \varphi_t)^{3/2} - (\psi_{ss} - \varphi_t)^{3/2}\Big]$$

$$I_{Diff} = \varphi_t\Big(\psi_{sd} - \psi_{ss} + \gamma\Big(\sqrt{\psi_{sd} - \varphi_t} - \sqrt{\psi_{ss} - \varphi_t}\Big)\Big)$$

$$(V_{gb} - \varphi_{ms} + \varphi_{nt} - \psi_s)^2 = \gamma^2 \cdot \varphi_t H(u)$$

$$\varphi_{nt} = \frac{q}{C_{ox}}(N_{ot} - D_{it} \cdot (\psi_s - \varphi_b))$$

Fit w/ analytical model

| Dose [krad(Si)] | N <sub>ot</sub> (cm <sup>-2</sup> ) | D <sub>it</sub> (cm <sup>-2</sup> /V) |

|-----------------|-------------------------------------|---------------------------------------|

| 200             | 1.92x10 <sup>12</sup>               | 2.6x10 <sup>11</sup>                  |

| 500             | 2.39x10 <sup>12</sup>               | 6.0x10 <sup>11</sup>                  |

| 1000            | 2.75x10 <sup>12</sup>               | 8.0x10 <sup>11</sup>                  |

Fit based on approximations for oxide thickness, body doping, workfunction, etc.

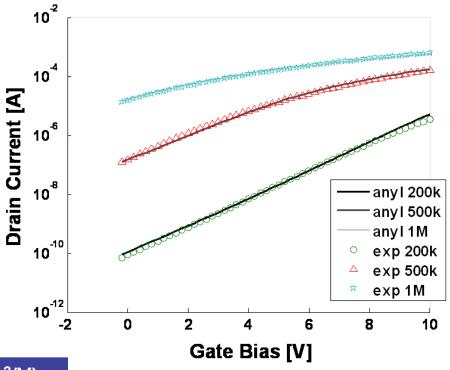

## **TCAD Validation**

#### TCAD sims performed on FOXFET structure validate fit

#### Fit w/ TCAD model

| Dose [krad(Si)] | N <sub>ot</sub> (cm <sup>-2</sup> ) | D <sub>it</sub> (cm <sup>-2</sup> /V) |

|-----------------|-------------------------------------|---------------------------------------|

| 200             | 1.82x10 <sup>12</sup>               | 2.99x10 <sup>11</sup>                 |

| 500             | 2.29x10 <sup>12</sup>               | 6.89x10 <sup>11</sup>                 |

| 1000            | 2.65x10 <sup>12</sup>               | 9.18x10 <sup>11</sup>                 |

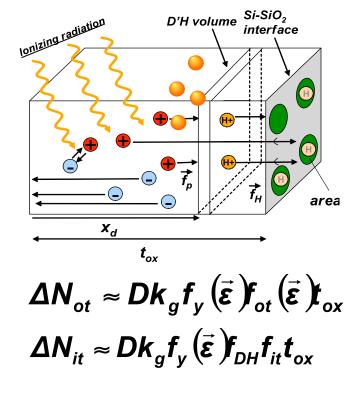

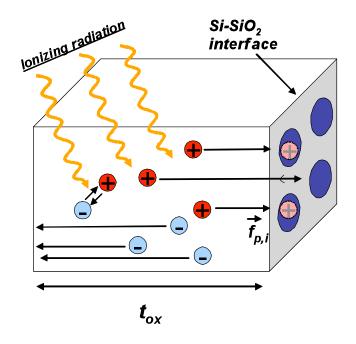

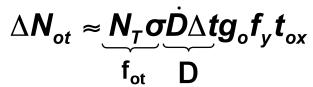

# Analytical Defect Model (simplified)

#### Simple analytical model shows linear dependence on dose

$$f_{ot} = 0.45$$

## Reasons for model discrepancy

## Simple model neglects:

- Effect of precursor limit (saturation cannot be accurately reproduced by the model)

- Effect of trapped charge annealing (anneal rate insufficient to explain saturation)

- Effect of field inversion and electron trapping (most promising mechanism for modeling saturation)

Pre-cursor limit factor

$$\frac{\partial N_{ot}}{\partial t} = (N_T - N_{ot}(t))\sigma f_p$$

$$-\frac{N_{ot}(t)}{\tau_k}$$

Anneal factor

basis for revised model

### **Revised Model Additions**

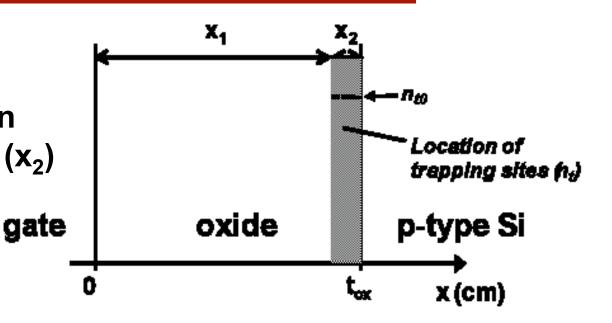

Volumetric, uniform precursor distribution (n<sub>T</sub>) at fixed distance (x<sub>2</sub>) from interface

Electron compensation term added to volumetric charge build-up model

$$\Delta n_{ot} = \dot{D} \Delta t g_0 \left( n_T \sigma_p f_{y,p} x_p - n_{ot} \sigma_n f_{y,n} x_n \right)$$

e- trapping term added

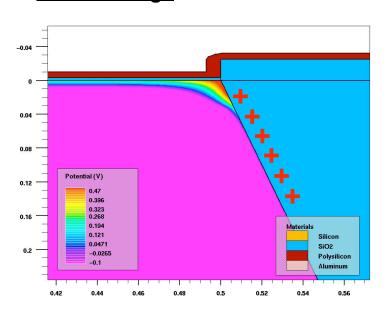

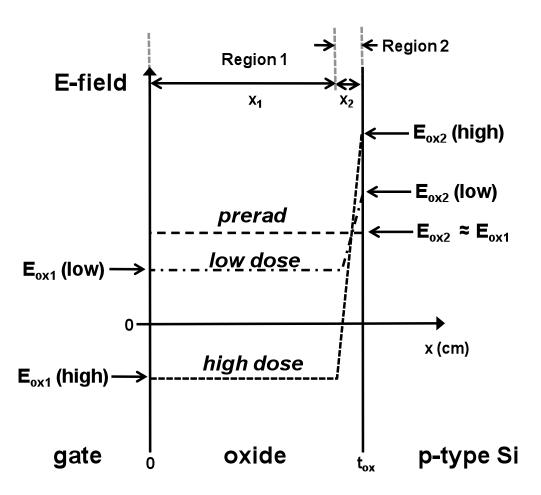

### Oxide Field Inversion

- At low TID oxide field directed toward p-Si

- At high TID, oxide field in reg. 1 inverts

$$E_{ox2} = \left(V_{gb} - \varphi_{ms} - \varphi_{nt} - \psi_{s}\right)/t_{ox}$$

$$E_{ox2} = E_{ox1} + \frac{qn_{ot}}{\varepsilon_{ox}}x_{2}$$

### Full Model

$$\Delta n_{ot} = \begin{cases} \dot{D}\Delta t g_{o} \left( n_{T} \sigma_{p} f_{y} \left( E_{ox1} \right) t_{ox} - n_{ot} \sigma_{n} f_{y} \left( E_{ox3} \right) x_{2} \right) E_{ox1} > 0 \\ \dot{D}\Delta t g_{o} \left( n_{T} \sigma_{p} f_{y} \left( E_{ox3} \right) x_{2} - n_{ot} \sigma_{n} f_{y} \left( E_{ox1} \right) t_{ox} \right) E_{ox1} < 0 \end{cases}$$

$$E_{\text{ox3}} = \frac{E_{\text{ox1}} + E_{\text{ox1}}}{2}$$

$$\Delta N_{ot} = \Delta n_{ot} \cdot x_2 \left( 1 - \frac{x_2}{2t_{ox}} \right)$$

$$N_{ot}(t) = N_{ot}(t - \Delta t) + \Delta N_{ot}$$

Model computes oxide trapped charge density  $\Delta N_{ot} = \Delta n_{ot} \cdot x_2 \left( 1 - \frac{x_2}{2t_{ox}} \right)$  iteratively after specified irradiation time

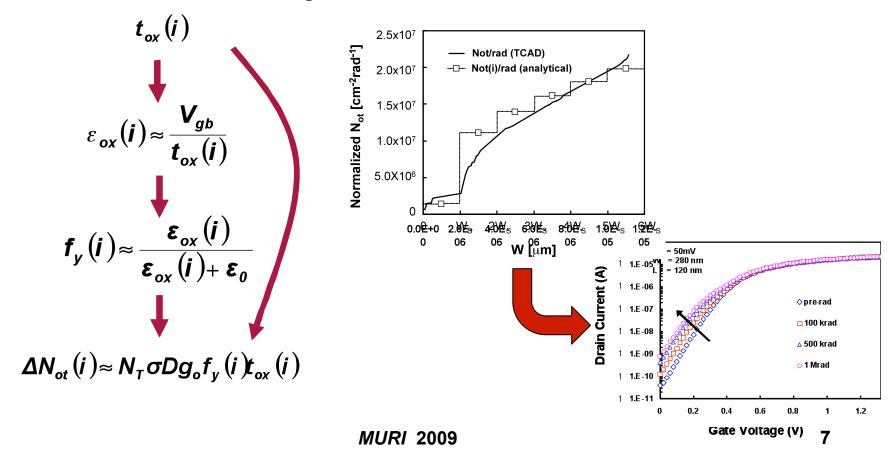

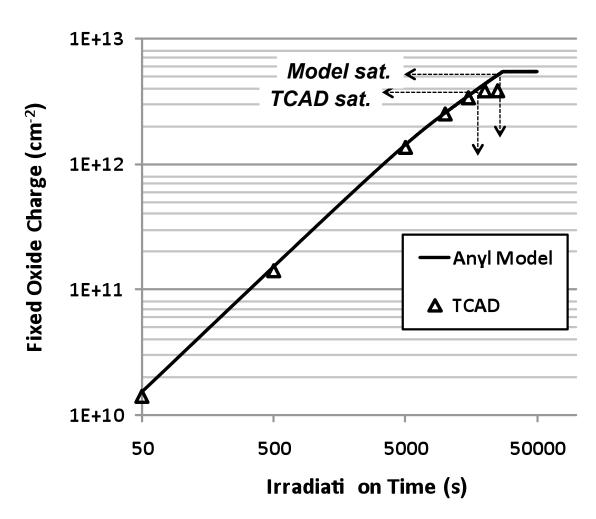

## Revised Analytical Model vs. TCAD

- TCAD computes N<sub>ot</sub> from REM simulator in Silvaco

- Model and TCAD use same parameters and function, i.e.,  $n_T$ ,  $\sigma_n$ ,  $\sigma_p$ , and  $f_y$

- Identical results except TCAD saturation occurs slightly before the model

Slight discrepancy likely due to error near zero field inversion point (under investigation) ... but results are very promising!

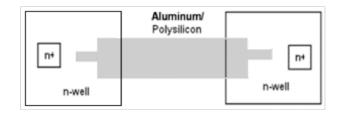

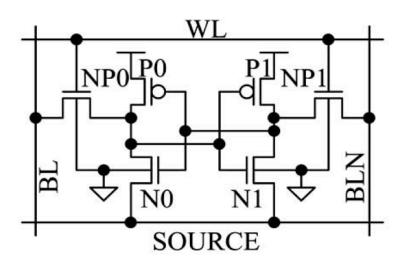

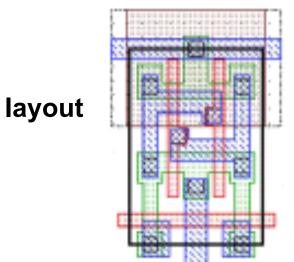

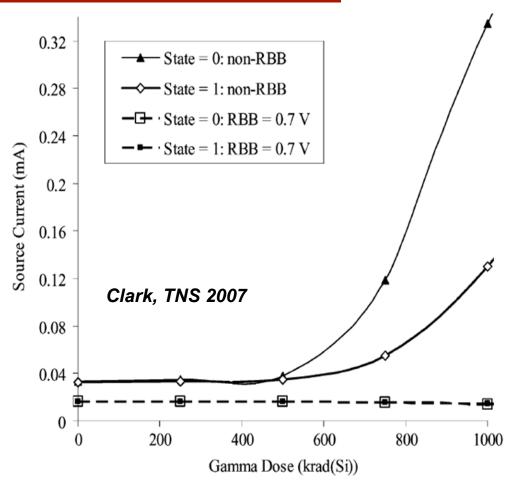

# Circuit Demonstration: SRAM leakage mitigation with RBB

#### 6T SRAM w/ nFET body control

With reverse body bias (RBB), radiationinduced supply current to cell suppressed, but do we really need 0.7V RBB??

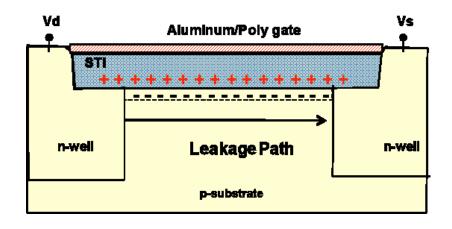

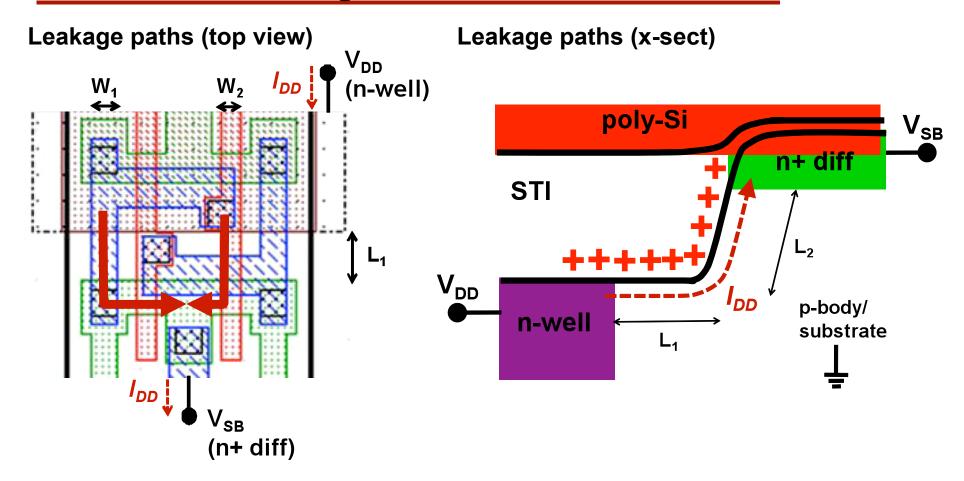

# SRAM leakage mechanism: inter-device field oxide leakage

20

Through analysis of SRAM response, n-well to n+ diffusion interdevice leakage identified as mechanism for increased supply current at high TID levels

MURI 2009

### **TID** analytical model implementation

#### Model enables:

- fit to non-RBB high dose response when  $V_{SB} = 0V$

- •identification of V<sub>SB</sub> sufficient to suppress field oxide leakage

Use of model supports optimization of RHBD designs ... important when considering tradeoff between RBB and SEEs!

## **Summary: Analytical Model**

- Discrepancies between saturated defect densities extracted from data and those calculated using simple trapping model suggest need for model revisions

- While charge annealing and precursor limits can cause saturation, the inclusion of field inversion with electron compensation models most effective in reproducing data

- Revised approach can be implemented easily as a compact model to enable estimates of circuit response to TID and support design optimization

# Recent Work (2009)

- Demonstration of analytical model of TID effects on bulk CMOS isolations oxides

- Revised analytical model for TID defect buildup compared to FOXFET I-V and TCAD simulations

- Demonstration of modeling approach: SRAM with reverse body bias

- Effects of Channel Implant Variation on Edge Leakage Currents

- Modeling TID effects in Multiple Gate FETs

## **Motivation of Study**

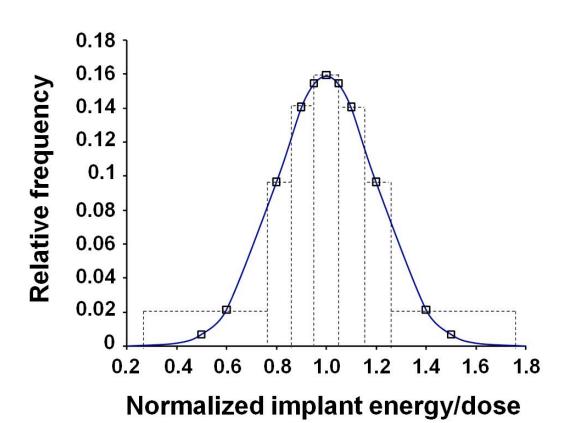

- To model the effects of statistical variation in the dose and energy of MOSFET channel implants on radiation-induced edge parasitics

- 90 nm commercial bulk CMOS technology

Results show a slight variability in channel implant parameters can have a significant impact on doping levels and thus edge leakage currents

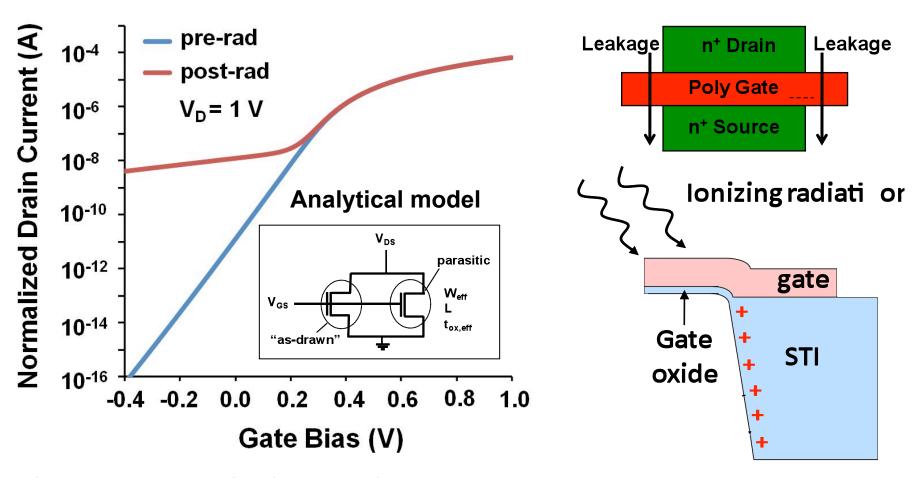

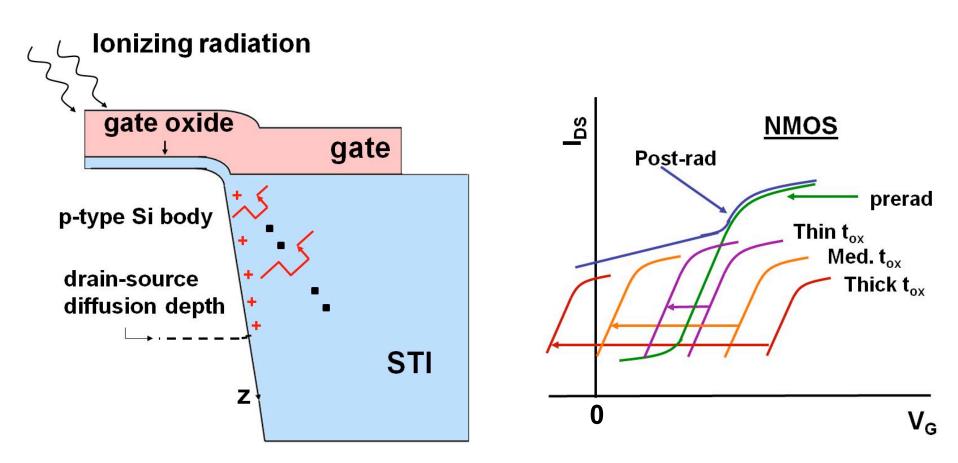

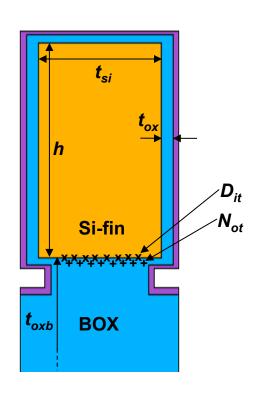

## Radiation-induced edge leakage

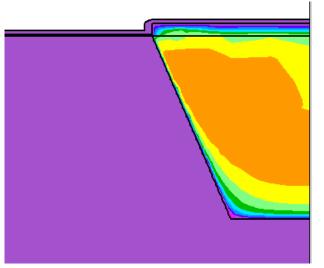

Charge buildup ( $N_{ot}$ ) in the STI inverts the sidewall and induces a parasitic leakage path along the edges of the "as-drawn" transistor

## **Parasitic Edge Devices**

Increased exposure to TID leads to formation of parasitic edge devices (with varying  $t_{ox}$ ) operating in parallel with "as-drawn" FET

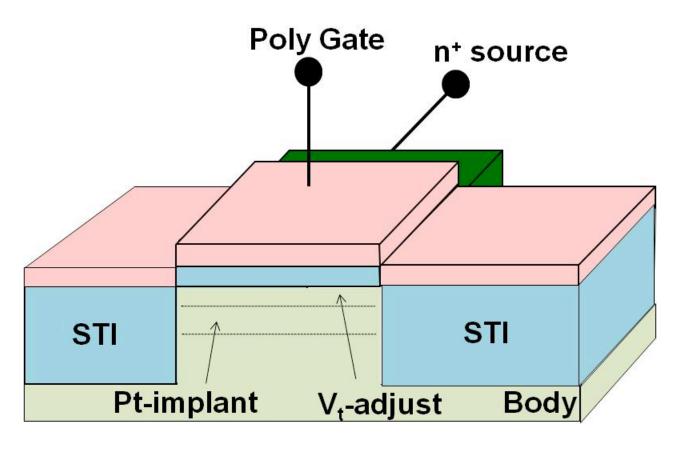

## **MOSFET Channel Implants**

Doping along sidewall is determined by dose and energy of punchthrough (Pt), threshold-adjust ( $V_t$ -adjust), and sidewall implants

## **Channel Implant Variation**

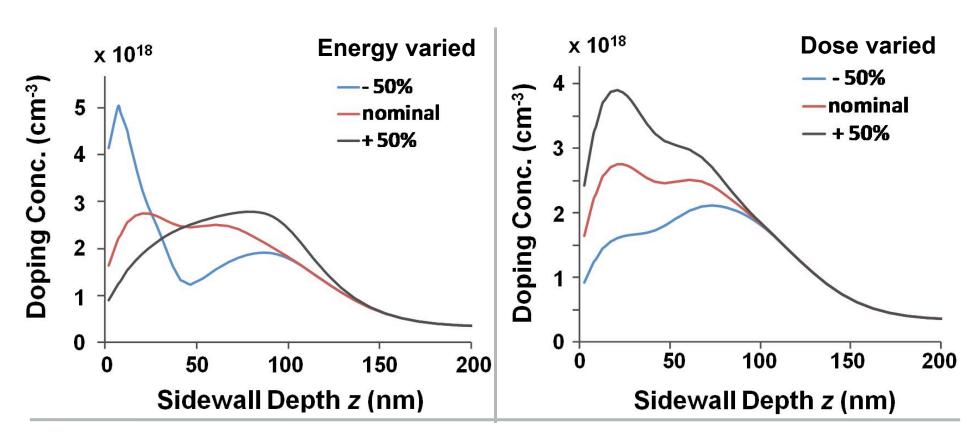

- Statistical variations in dose and energy of channel implants alter doping along STI sidewall

- Doping profiles obtained using process simulator

- Nominal values for dose and energy are 1.25 x 10<sup>13</sup> cm<sup>-2</sup> and 4 keV (V, implant)

Bernstein et al., found a normal distribution in the threshold voltage when testing N number of devices (IBM J. RES. & DEV., 2006)

# **Impact on Doping Profile**

Effect of statistical variations in dose and energy of the V<sub>t</sub>-adjust implant on doping profiles along STI sidewall

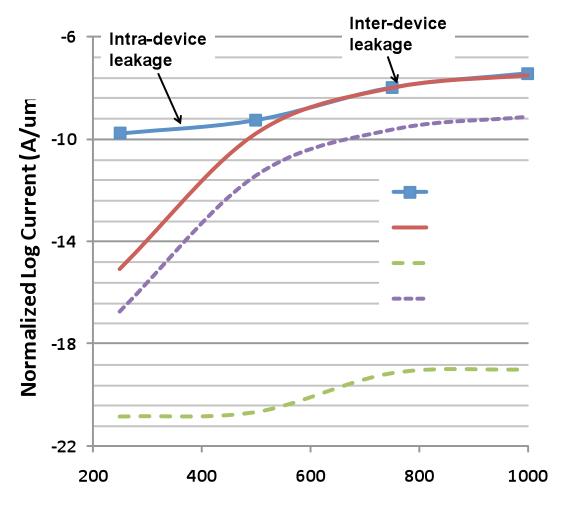

# Off-state Leakage Current

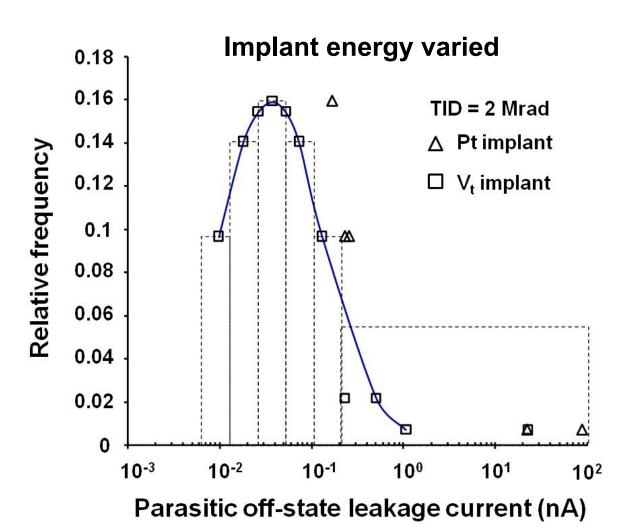

- Off-state leakage is I<sub>D</sub>

@ V<sub>G</sub> = 0 V

- Distribution in radinduced edge leakage currents for variations in the energy of the V<sub>t</sub>adjust and Pt implants

# Off-state Leakage Current

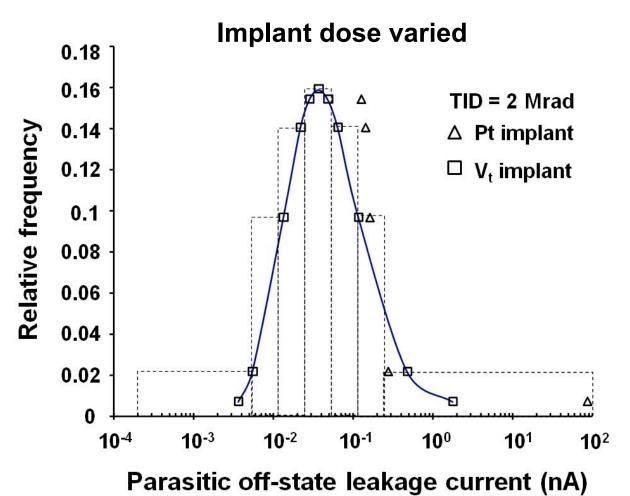

- Off-state leakage is I<sub>D</sub>

@ V<sub>G</sub> = 0 V

- Lognormal distribution in rad-induced leakage currents for variations in the implant dose of the V<sub>t</sub> and Pt implants

# Summary: Implant Variation Effects

- Statistical variations in dose and energy of MOSFET channel implants impact doping along STI sidewall and thus amount of edge leakage current

- Results demonstrate large spread in leakage currents from a fairly tight normal distribution in process parameters

# Recent Work (2009)

33

- Demonstration of analytical model of TID effects on bulk CMOS isolations oxides

- Revised analytical model for TID defect buildup compared to FOXFET I-V and TCAD simulations

- Demonstration of modeling approach: SRAM with reverse body bias

- Effects of Channel Implant Variation on Edge Leakage Currents

- Modeling TID effects in Multiple Gate FETs

MURI 2009

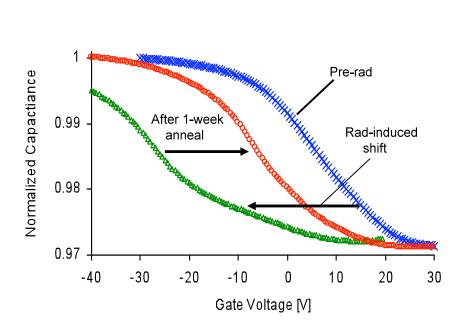

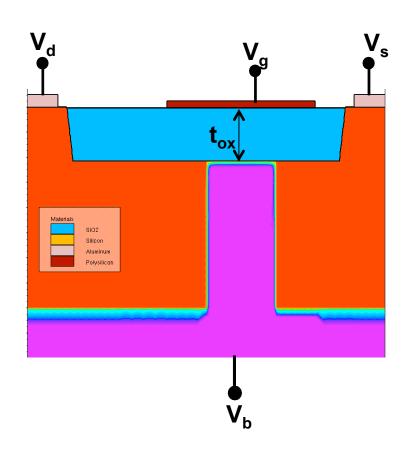

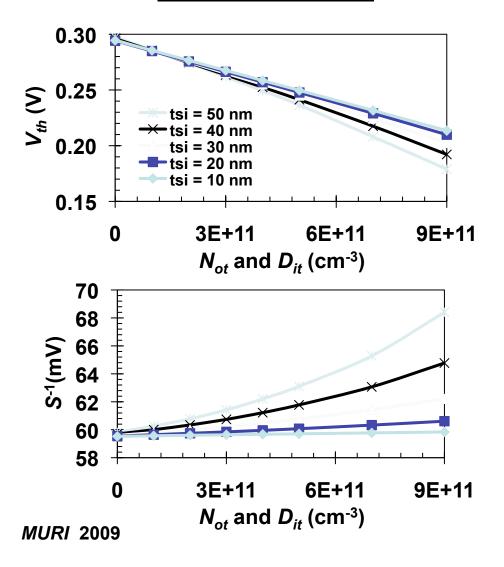

### TID effects in MuGFET SOI devices

Devices with narrower fins exhibit less degradation with TID as observed by  $\Delta V_{th}$  and  $\Delta S^{-1}$  as a function of  $N_{ot}$  and  $D_{it}$

#### **Simulation results**

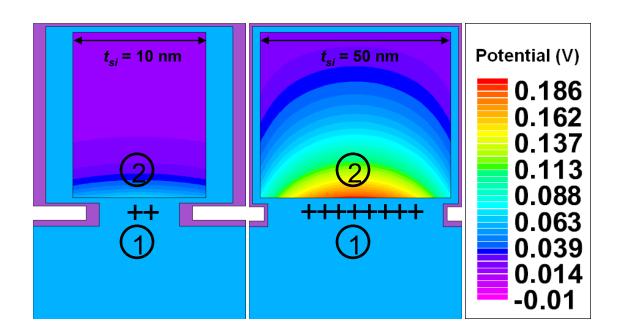

## Why narrow fins are harder

- 1. Electric field near fin-BOX interface of device with narrow fins is reduced by influence of the lateral gates. This reduces the charge yield

- 2. Devices with narrow fins have an improved control over the electrostatic potential inside the fin due to the lateral gates

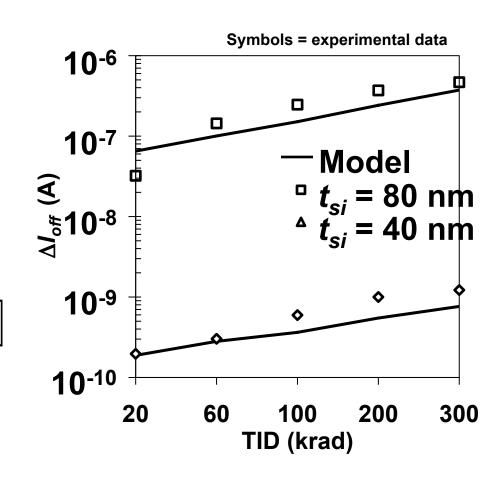

## MuGFET TID Model

- $I_{d}$ - $V_{gs}$  degradation modeled analytically to predict  $\Delta I_{off}$  as function of TID and  $t_{si}$ .

- Radiation-induced degradation parameters enter model through defect potential  $\phi_{nt}$  which is a function of  $t_{si}$ .

$$\phi_{nt}(t_{si}) = \phi_{nt0}[1 - \mathrm{DG}(t_{si})]$$

$$\phi_{nt0} = \frac{q}{C_{orf}} \left[ N_{ot} - D_{it} \left( \psi_b - \phi_f \right) \right]$$

• Parameters extracted to describe  $DG(t_{si})$  making the analytical model adaptable to different technologies.

## **Summary: TID effects in MugFETs**

- Modeling results support data (EI-Mamouni)

- Thinner fins in MugFETs lead to less defect buildup in BOX and increased charge masking from lateral gates (i.e. thinner fins = harder parts)

- Surface potential based model can accurately reproduce experimental date