EECE 285 – VLSI Design

## **Cadence Tutorial**

EECE 285 VLSI

By: Kevin Dick Co-author: Jeff Kauppila Co-author: Dr. Arthur Witulski

| Purpose of Cadence                                 |                  |       |

|----------------------------------------------------|------------------|-------|

| 1) The Purpose of Cadence                          |                  | pg. 4 |

| Linux                                              |                  |       |

| 1) The Purpose of Linux                            |                  |       |

| 2) Basic Linux commands for r                      | unning cadence   |       |

| 3) Logging onto cadence                            |                  |       |

| 4) Lock files                                      |                  |       |

| Navigating in Cadence                              |                  |       |

| 1) Icfb log                                        |                  | pg. 3 |

| 2) Library Manager                                 |                  |       |

| 3) Schematic, symbol and layou                     | ut editing       | pg. 3 |

| Building a schematic (using in                     | nverter example) |       |

| 1) Creating a new library                          | <b>1</b>         |       |

| 2) Creating a new cell view                        |                  |       |

| 3) Making the schematic                            |                  |       |

| 4) Printing the schematic                          |                  |       |

| Building a symbol                                  |                  |       |

| 1) Building the symbol for the                     | schematic        |       |

| Testing the circuit                                |                  |       |

| 1) Setting up the test circuit                     |                  |       |

| <ol> <li>2) Simulating the test circuit</li> </ol> |                  |       |

| Designing the layout                               |                  |       |

| 1) Opening layout file                             |                  |       |

| 2) Setting up the parameters                       |                  |       |

| 3) Setting up the connections                      |                  |       |

| 4) Running DRC (Design Rule                        | Checker)         |       |

| 5) Extracting the circuit                          | <i>*</i>         |       |

| 6) Running LVS (Layout versu                       | s Schematic)     |       |

# Hooking up the padframe 1) Fdsa

- 2) Fdasfds

- 3) Fdsafd

## Submitting the project to MOSIS

- 1) Extracting the CIF file

- 2) Running checksum and count

- 3) Setting up an account

- 4) Filling out the paper work

### **Design Rules**

1) MOSIS design rules for 0.5µm technology

pg. 6-9

### **Purpose of Cadence**

Cadence is an Electronic Design Automation (EDA) environment in which different applications and tools can are integrated together. This allows all the stages of IC design and verification to be done in a single environment. The different tools are supported by different fabrication technologies allowing for customization of the Cadence environment to fit the particular technology.

### Linux

- Linux is an operating system that is a multi-user, multi-tasking system that can be used on servers, desktops and laptops. Linux was originally developed at Bell Labs in 1969. Linux is used to access cadence and manage the files in its libraries.

- 2) Basic Linux commands used for running cadence

- A) Command: ls

Function: lists the files in the current directory Example: ls

B) Command: pwd

Function: tells you what directory you are currently in Example: pwd

C) Command: mkdir Function: makes a new directory

Example: mkdir project (makes a new directory called project)

- D) Command: cd

Function: takes into the specified directory

Example: cd NCSU AMI06 (takes you into the directory called NCSU AMI06)

- E) Command: cd ..Function: takes you back one directory Example: cd ..

- F) Command: mv

Function: moves a directory to the specified location

Example: mv adder adder2 (moves the directory adder to the current directory and changes the name to adder2)

- G) Command: cp

- Function: copies a file

Example: cp ../multi . (copies the file named multi from the previous directory to the current directory)

H) Command: gzip

Function: compresses files, so they take up less space Example: gzip inv (compresses the file called inv)

I) Command: gunzip

Function: uncompresses files that have been compressed by the command gzip

Example: gunzip inv.gz (uncompresses the file named inv.gz)

- J) Command: chmod

Function: changes the read, write and execute permissions on the files

Example: chmod nand (lets you change the read, write and execute permission for the file named nand)

- K) Command: rm

Function: removes a file

Example: rm nor.zip (removes the file named nor.zip)

L) Command: diff

Function: compares two files and shows their differences

Example: diff or and (compares the files called or and and showing their differences)

M) Command: clear Function: clears the screen

Example: clear

N) Command: tar -cvf

Function: combines many files or directories into one file Example: tar –cvf homework3.tar layout schematic symbol (combines the directories names layout, schematics and symbol into one and names it homework3.tar)

O) Command: rmdir

Function: removes a directory that is empty

Example: rmdir pad (removes the directory called pad)

P) Command: zip

Function: zips up a fileExample: zip add lock (zips up the file named add and saves it as lock.zip)

Q) Command: --help

Function: Tells you the function of a command Example: chmod –help (tells you the function of the command chmod)

R) Command: zip –r

Function: zips up a directory

Example: zip –r Bickham\_HW4 Bickham\_HW4 (zips up the directory named Bickham\_HW4 and saves it as Bickham\_HW4.zip)

- S) Command: unzip

Function: unzips a file that has been zipped up by the zip command (ends in .zip)

Example: unzip Homework4.zip (unzips the file named Homework4.zip)

- T) Command: tar –xvf

Function: separates files or directories that have been combined by the tar –cvf command

Example: tar –xvf Homework1.tar (separates the directories and files that have are combined in the Homework1.tar file)

U) Command: rm –r Function: removes a directory and its contents

Example: rm -r nor (removes the directory called nor and all of its contents

V) Command: cp-r

Function: copies a directory and all of its contents

Example: cp –r HW5 (copies the directory called HW5 and all of its contents)

W) Command: history

Function: shows the list of the last 100 commands Example: history

X) Command: find

Function: searches the current directory and all subdirectories for the specified file(s) Example: find project3 (searches the current directory and all subdirectories for files called project3)

- Y) Efads

- Z) Fewfds

AA)

3) Logging onto cadence

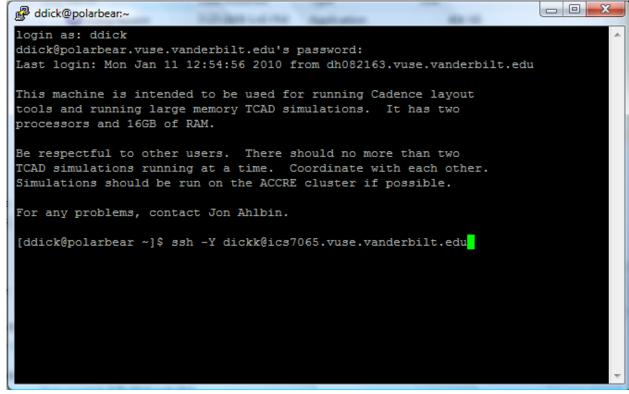

3.1) To log into cadence log onto polarbear and then a campus machine by using the ssh – Y command.

Figure 1: logging onto a campus computer

Here is a list of the campus machines:

ics7055.vuse.vanderbilt.edu ics7056.vuse.vanderbilt.edu

ics7057.vuse.vanderbilt.edu ics7058.vuse.vanderbilt.edu ics7059.vuse.vanderbilt.edu ics7060.vuse.vanderbilt.edu ics7061.vuse.vanderbilt.edu ics7062.vuse.vanderbilt.edu ics7063.vuse.vanderbilt.edu ics7064.vuse.vanderbilt.edu ics7066.vuse.vanderbilt.edu ics7067.vuse.vanderbilt.edu ics7069.vuse.vanderbilt.edu ics7070.vuse.vanderbilt.edu ics7070.vuse.vanderbilt.edu ics7071.vuse.vanderbilt.edu

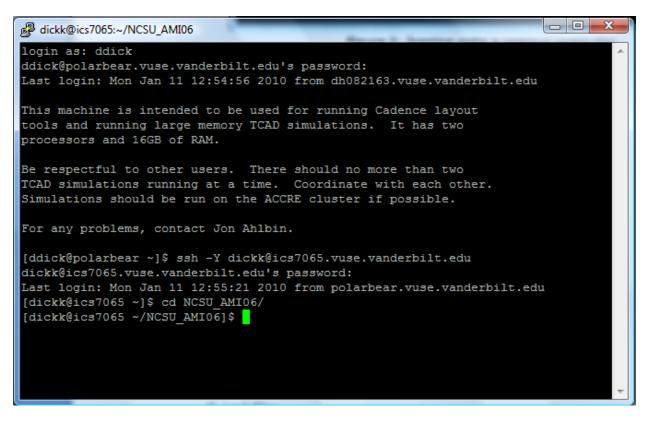

Next, you need to go into the NCSU\_AMI06/ directory.

Figure 2: The NCSU\_AMI06/ directory

Then, use the command **exec /bin/bash**. In bash, use the command **source soureme.sh** and then **icfb**. This will log you into cadence.

VANDERBILT UNIVERSITY

### EECE 285 - VLSI Design

### - O X dickk@ics7065:~/NCSU\_AMI06 login as: ddick ddick@polarbear.vuse.vanderbilt.edu's password: Last login: Mon Jan 11 12:54:56 2010 from dh082163.vuse.vanderbilt.edu This machine is intended to be used for running Cadence layout tools and running large memory TCAD simulations. It has two processors and 16GB of RAM. Be respectful to other users. There should no more than two TCAD simulations running at a time. Coordinate with each other. Simulations should be run on the ACCRE cluster if possible. For any problems, contact Jon Ahlbin. [ddick@polarbear ~]\$ ssh -Y dickk@ics7065.vuse.vanderbilt.edu dickk@ics7065.vuse.vanderbilt.edu's password: Last login: Mon Jan 11 12:55:21 2010 from polarbear.vuse.vanderbilt.edu [dickk@ics7065 ~]\$ cd NCSU AMI06/ [dickk@ics7065 ~/NCSU AMI06]\$ exec /bin/bash bash-4.0\$ source sourceme.sh bash-4.0\$ icfb&

Figure 3: Logging into cadence

#### 4) Lock files

4.1) If your file says "edit mode only" or otherwise does not respond, there is a good chance you have a .cdslck lock on your schematic or layout file. So, before you start and before you source the sourceme.sh file, type: find \$HOME -name \\*.cdslck

The find command should show you where the cdsclk files are in your directory. Delete (rm) these files, then you shouldn't have any trouble till the next time it locks the files.

### Navigating in Cadence

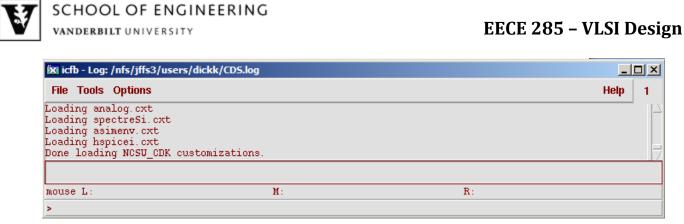

The icfg log is the window that gives you gives you a list of the actions that have taken place in cadence, Figure 1. This most recent action is at the bottom of the list. This is where you go to see the result of DRC and LVS checks. The file tab allows you to create a new library or cell, import files, export files and open files in the library manger. The tools tab gives you a list of the different tools that are available in cadence. The options tab allows you to save the session and change the preferences.

Figure 1: Icfb log

2) The library manager is where the libraries, cells and views are stored, Figure 2. If you select a cell of one of the libraries you can view the different layouts (schematic, extracted, layout, symbol, etc.) of that cell, by double clicking on the type of view. The file tab allows you to create a new library, cell view and category, open a cell view, load or save defaults or exit. The edit tab allows you to copy, rename, delete, change properties, access permission and library path.

VANDERBILT UNIVERSITY

| 🗙 Library Manager: Directorys/jffs3/users/dickk/NCSU_AMI06                                                                                                                                                                                                                                              |                                                                                                                                                                                             |                                                                             |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|

| <u>File Edit View D</u> esign Mar                                                                                                                                                                                                                                                                       | nager                                                                                                                                                                                       | <u>H</u> elp                                                                |  |  |  |  |  |  |

| 🔲 Show Categories 📃 Show                                                                                                                                                                                                                                                                                | v Files                                                                                                                                                                                     |                                                                             |  |  |  |  |  |  |

| Library                                                                                                                                                                                                                                                                                                 | Cell                                                                                                                                                                                        | - View                                                                      |  |  |  |  |  |  |

| 0SU_stdcells_ami05_h                                                                                                                                                                                                                                                                                    | JA0122X1                                                                                                                                                                                    | T                                                                           |  |  |  |  |  |  |

| MOSIS_Layout_Test<br>NCSU_Analog_Parts<br>NCSU_Digital_Parts<br>NCSU_TechLib_ami06<br>NCSU_TechLib_tami06<br>NCSU_TechLib_tamc02<br>NCSU_TechLib_tsmc02d<br>NCSU_TechLib_tsmc03<br>NCSU_TechLib_tsmc03d<br>NCSU_TechLib_tsmc04_4M2H<br>OSU_stdcells_ami05_h<br>US_8ths<br>ahdlLib<br>analogLib<br>basic | AA_README<br>AND2X1<br>AND2X1<br>AND2X2<br>AOI21X1<br>AOI22X1<br>BUFX2<br>BUFX4<br>CLKBUF1<br>CLKBUF2<br>CLKBUF3<br>DFFNEGX1<br>DFFNEGX1<br>DFFSR<br>FAX1<br>FILL<br>HAX1<br>INVX1<br>INVX2 | abstract<br>extracted<br>functional<br>hdl<br>layout<br>schematic<br>symbol |  |  |  |  |  |  |

| Messages                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                             |                                                                             |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                         | fs/jffs3/users/dickk/NCSU_AMI<br>libFile //nfs/jffs3/users/dic                                                                                                                              |                                                                             |  |  |  |  |  |  |

| 5                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                             |                                                                             |  |  |  |  |  |  |

Figure 2: Library Manager

3) The virtuoso schematic editing window is where the schematic is built. The buttons on the left side are common used commands. To select an object, make sure that you do not have other commands running by hitting the Esc button on the keyboard, and run the cursor over the object and click on it, Figure 1.

Figure 1: Selecting an object

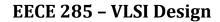

There is a list of short hand keyboard commands that allows you to quickly call the command. For example "m" is short for move, which will allow you to move an object. These short keyboard commands can be found by going to the tabs at the top of the window and looking at the right of the command, Figure 2.

Figure 2: Finding the short cut keyboard commands

To move an object around go to the edit tab and select move, or use the short command of "m", and select the object you wish to move. To delete an object you can click on the

button to the left of the window and click on the object, select the object and hit the delete button and the keyboard, or go to the edit tab and select the delete command and click on the object you wish to delete. If you drag the pointer across the buttons on the left

The

side of the screen they will give a description for what they do

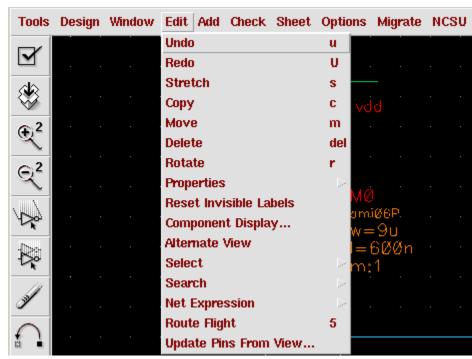

virtuoso symbol editing window is very similar to the virtuoso schematics editing window. The symbol editing window is laid out the same way but has less functions. The virtuoso layout editing window has is similar to the virtuoso schematic editing window but it also has a LSW window that appears with it. This window is to select the different layers to the parts of the transistor and connections between them. To select a layer, click on it in the LSW window and then go to the virtuoso layout editing window and draw the rectangle for that layer.

SCHOOL OF ENGINEERING VANDERBILT UNIVERSITY

| Sort Edit        | Help   |

|------------------|--------|

| 💹 pwell          | drw    |

| NCSU_TechLib     | _ami06 |

| Show Object      | :ts    |

| 📕 Inst 📕 Pin     |        |

| AV NV AS         | NS     |

|                  |        |

| 💹 pwell          | drw    |

| mvell            | drw    |

| active           | drw    |

| mactive          | drw    |

| pactive          | drw    |

| nselect          | drw    |

| pselect          | drw    |

| poly             | drw    |

| 🗱 elec           | drw    |

| metal1           | drw    |

| 🚾 metal2         | drw    |

| 💋 metal3         | drw    |

| cc               | drw    |

| via              | drw    |

| 💓 🕶 via2         | drw    |

| 🚻 glass          | drw    |

| <b>∿ highres</b> | drw    |

| Nodrc            | drw    |

| nolpe            | drw    |

If you want to view only one layer, select a layer from the LSW window and click on NV, which will select only that layer.

VANDERBILT UNIVERSITY

Figure 6: Selecting only one layer

Then go to the virtuoso layout editing window and click only that layer that was selected in the LSW window.

. This will let you view

**EECE 285 – VLSI Design**

| Tools   | Design | Window | Create | Edit | Verify | Connectivity | Options  | Routing | Migrate | Pcell    | Help  |

|---------|--------|--------|--------|------|--------|--------------|----------|---------|---------|----------|-------|

| ۲       | · · ·  |        |        |      |        |              |          |         |         | • •      |       |

|         |        |        |        |      |        |              |          |         |         |          |       |

| Q       |        |        |        |      | *      |              |          |         |         |          | · · · |

|         |        |        |        |      |        |              |          |         |         |          |       |

| ¢       |        |        |        |      |        |              |          |         |         |          |       |

| ତ୍      |        |        |        |      |        |              |          |         |         |          |       |

| ~       |        |        |        |      |        |              |          |         |         |          |       |

|         |        |        |        |      |        |              |          |         |         |          |       |

| ШQ      |        |        |        |      |        |              |          |         |         |          |       |

|         |        |        |        |      |        |              |          |         |         |          | · · · |

| Ū,      |        |        |        |      |        |              |          |         |         |          |       |

| 34      |        |        |        |      |        |              | · · ·    |         |         |          |       |

|         |        |        |        |      |        |              |          |         |         |          |       |

| $\cap$  |        |        |        |      |        |              |          |         |         |          |       |

|         |        |        |        |      |        |              |          |         |         |          | · · · |

|         |        |        |        |      |        |              |          |         |         |          |       |

| E. C.C. |        |        |        |      |        |              | · · ·    |         |         |          |       |

| ٦,      |        |        |        |      |        |              |          |         |         |          |       |

|         |        |        |        |      |        |              |          |         |         |          |       |

| S.      |        |        |        |      |        |              |          |         |         |          | · · · |

| [abcd]  |        |        |        |      |        |              |          |         |         |          |       |

| [verse] |        |        |        |      |        |              |          |         |         | <u> </u> | <br>  |

|         |        |        |        |      |        |              | <b>.</b> | •       | • 1     |          | <br>  |

Figure 7: Viewing a single layer

## **Building a schematic**

Creating a new library is the first part in building a new schematic. You can do this in one of two ways, first you can create a new library from the Library Manager, or the CIW. In either case select File->New->Library. This will bring up the create library window, Figure 1. Enter the name of the new library, for example digital\_lib, and select Attach Existing Library. When there is no path entered, it will place the library in the directory from which you started Cadence. If you started Cadence correctly, this will be your Working Directory.

| 🔀 New Libra        | ary                    | × |

|--------------------|------------------------|---|

| - Library          |                        | _ |

| Name               | digital_lib            |   |

| Directory          | y .                    |   |

| <br>LVS<br>spectre | . runl                 |   |

| }/jffs3,           | /users/dickk/NCSU_AMIO | Ğ |

| — Design           | Manager                |   |

| O Use              | NONE                   |   |

| () Use (           | ło DM                  |   |

| ОК                 | Apply Cancel Hel       | p |

Figure 1: Create New Library Window

Next, select **Attach to existing tech library** and select one of the available libraries. Remember which one was selected because it will be required for simulation later, Figure 2.

| 🐹 Tech  | nology File for New Library                | ×    |  |  |  |  |  |  |  |

|---------|--------------------------------------------|------|--|--|--|--|--|--|--|

| ок      | Cancel                                     | Help |  |  |  |  |  |  |  |

| Techno  | Technology File for library "digital_lib5" |      |  |  |  |  |  |  |  |

| If you  | will be creating mask layout               | or   |  |  |  |  |  |  |  |

| other   | physical data in this library, y           | ou   |  |  |  |  |  |  |  |

| will ne | eed a technology file. If you pl           | an   |  |  |  |  |  |  |  |

| to use  | e only schematic or HDL data,              | a    |  |  |  |  |  |  |  |

| techn   | ology file is not required.                |      |  |  |  |  |  |  |  |

| You c   | You can: 🔷 Compile a new techfile          |      |  |  |  |  |  |  |  |

|         | Attach to an existing techfile             |      |  |  |  |  |  |  |  |

|         |                                            |      |  |  |  |  |  |  |  |

Figure 2: Attaching a techfile

2) The next step to creating a schematic is creating a new Cell View. This is done in the Library Manger, but it can be done it two ways. First, select the Library in which you will be adding this Cell. Second, either select File->New->Cell View from the Library Manger or you can type the name of the new cell in the blank under Cell in the Library Manger and hit the enter key. This will bring up a window in which you can specify the type of view you are creating, Figure 3. Since we are creating an inverter, we will name the Cell inv. It is good to give the cell a name that will help you remember what is in it.

| a         | Ci       | Create New File      |      |  |  |  |  |  |  |  |

|-----------|----------|----------------------|------|--|--|--|--|--|--|--|

| ОК        | Cancel   | Defaults             | Help |  |  |  |  |  |  |  |

| Library N | tame _   | digital_lib          | -    |  |  |  |  |  |  |  |

| Cell Nam  | e i      | inv                  |      |  |  |  |  |  |  |  |

| View Na   | me 「     | schenatid            |      |  |  |  |  |  |  |  |

| Tool      | C        | Composer-Schematic 🚙 |      |  |  |  |  |  |  |  |

| Library p | ath file |                      |      |  |  |  |  |  |  |  |

Figure 3: Create New Cell Window

In the **Create New File window**, select as the tool **Composer-Schematic**. This will cause the View Name to be automatically filled with the name **schematic**. When you are finish click the **OK** tab. This will close the current window and bring up the window in which we will design the schematic of the Inverter.

3) Now we are ready to layout the schematic design of the Inverter. After creating the new cell, a window opens in which we will create our schematic, Figure 4. This window is the Virtuoso Schematic Editing window.

VANDERBILT UNIVERSITY

### EECE 285 – VLSI Design

| <u></u>        |            |         |       |     |       | Virtuos | io® Schei | natic E | diting:     |          |                                 |        |

|----------------|------------|---------|-------|-----|-------|---------|-----------|---------|-------------|----------|---------------------------------|--------|

| Cmd            | <b>1</b> 0 | Sel:    | 0     |     |       |         |           |         |             |          |                                 | 2      |

| Tools          | Design     | Window  | Edit  | Add | Check | Sheet   | Options   | NCSU    |             |          |                                 | Help   |

| V              |            |         |       |     |       |         |           |         |             |          |                                 |        |

| ٢              |            |         |       |     |       |         |           |         |             |          |                                 |        |

| € <sup>2</sup> |            |         |       |     |       |         |           |         |             |          |                                 |        |

| Q2             |            |         |       |     |       |         |           |         |             |          |                                 |        |

|                |            |         |       |     |       |         |           |         |             |          |                                 |        |

| De 1           |            |         |       |     |       |         |           |         |             |          |                                 |        |

| 2              |            |         |       |     |       |         |           |         |             |          |                                 |        |

| ¥              |            |         |       |     |       |         |           |         |             |          |                                 |        |

| $\cap$         |            |         |       |     |       |         |           |         |             |          |                                 |        |

|                |            |         |       |     |       |         |           |         |             |          |                                 |        |

| Q              |            |         |       |     |       |         |           |         |             |          |                                 |        |

|                |            |         |       |     |       |         |           |         |             |          |                                 |        |

| <br>           |            |         |       |     |       |         |           |         |             |          |                                 |        |

| ebc.           |            |         |       |     |       |         |           |         |             |          |                                 |        |

| -              |            |         |       |     |       |         |           |         |             |          |                                 |        |

| •••            |            |         |       |     |       |         |           |         |             |          |                                 |        |

|                |            |         |       | Эť. |       |         |           |         | n el elle   | E 919-18 | 化生活剂 化间子化 医子宫下的 化化              |        |

| G              |            | showCli | ckInf | 0() |       |         | Mi a      | chHiMo  | usePopUp () |          | R:hiDisplayForm( NCSU_createLib | Porn ) |

Figure 4: Virtuoso Schematic Editing Window

The schematic level design is building the inverter from the transistor level. To add a component click **Add->Instance**. This brings up the Component Browser and a window in which you can specify the component to be added, Figure 5.

VANDERBILT UNIVERSITY

|                                 |           | T al                |                           |             | Add Ins        | Add Instance      |             |  |  |  |  |

|---------------------------------|-----------|---------------------|---------------------------|-------------|----------------|-------------------|-------------|--|--|--|--|

|                                 |           | Hide                | Cancel                    | Default     | s              |                   | H           |  |  |  |  |

|                                 |           | Library             | Library NCSU_Analog_Par   |             |                |                   | Browse      |  |  |  |  |

|                                 |           | Cell                | pmos4                     |             |                |                   |             |  |  |  |  |

|                                 |           | View                | symbol                    |             |                |                   | ĺ           |  |  |  |  |

|                                 |           | Names               | μ                         |             |                |                   | ĺ           |  |  |  |  |

|                                 |           | Array               |                           | Rows        | 1              | Columns           | 1           |  |  |  |  |

|                                 |           | Rota                | te                        | S           | lideways       | 1                 | Upside Down |  |  |  |  |

| Filter                          |           | Fingers<br>Width (g | rid units)                |             | 1<br>6<br>450. | On M              | _           |  |  |  |  |

| Uncategorized                   |           |                     | ស់លោកសា )                 |             | 450            | 500.05 <b>8</b> / | _           |  |  |  |  |

| CONTENTS                        | Ĩ         | 10000               | grid units)               |             | 4              |                   |             |  |  |  |  |

| Current_Sources<br>Diodes       |           | Length              |                           |             | 300n           | nį                |             |  |  |  |  |

| H_Spice_Only<br>Microwave_Parts | 6         | Longth (            | (maanaan)                 |             | 300n           | n                 |             |  |  |  |  |

| Misc_Parts<br>N Transistors     | Drain dif | fusion are          | a                         | 3.37        | 3.375e-13      |                   |             |  |  |  |  |

| P_Transistors                   |           | Source o            | liffusion a               | rea         | 3.37           | 5e-13             |             |  |  |  |  |

| Parasitic_Devic<br>R_L_C        | 83        | Drain dif           | Drain diffusion perimeter |             |                | 2.4u M            |             |  |  |  |  |

|                                 | Source    | liffusion p         | erimeter                  | 2.4u        | 2.4u M         |                   |             |  |  |  |  |

|                                 |           | Ource (             |                           | or mile vor | dimension of   |                   |             |  |  |  |  |

Figure 5: Component Browser and Add Instance Windows

The first to add is the nmost transistor. To select this transistor, select NCSU\_Analog\_Parts then select the category N\_Transistors and select the nmos4 transistor from the list. In the Add Instance window enter the width as 4u and the length as 2u. Cadence will automatically change this to 4u M and 2u M respectively. Move the cursor into the editing window. Notice that there is an nmos transistor there instead of the normal cursor. To place the component, you need to left click. To rotate the component you need to right click. To exit from adding the current component or any other action press the Esc key. Notice that there are letters next to many of the choices in the menus, these are hot keys and can make you work progress a lot faster if they are learned. Place the nmos transistor in the bottom half of the screen on the right side of the center line.

Next, we will add a pmos transistor. This is located under the library NCSU\_Analog\_Parts->P\_Transistors and select the pmos4. Give it the same width and length and place it on the top half of the screen above the nmos transistor.

The next step is to add the pins. Click **Add->Pin** and a window appears for adding pins to the schematic. We will add pins *vdd*, *vss*, *in*, and *out*. Ensure that the direction is set to inputOutput, Figure 6.

VANDERBILT UNIVERSITY

| A         |        |               | Add Pin      |                     |

|-----------|--------|---------------|--------------|---------------------|

| Hide      | Cancel | Defaults      |              | Help                |

| Pin Name  | s      | ydd vas in    | out          |                     |

| Direction |        | inputOutput 🚄 | Bus Expansio | an 🔹 off 🥪 on       |

| Usage     |        | schematic 💷   | Placement    | 🔹 single 🧹 multiple |

| Rotat     | e      |               | Sideways     | Upside Down         |

Figure 6: Add Pin Window

The order in which the pins are added does not matter. You can also add only one pin at a time. In the current method, the pins will be placed in the order they appear in the list. First, place the vdd pin above the pmos transistor. Note the small diamond that is the actual pin so rotate the object until the diamond faces down toward the pmos transistor. Add the vss below the nmos, the in to the left of the screen, and the out to the right of the screen. In all cases make sure the small diamond faces the transistors.

Now we will add wires to connect the entire Inverter so it will work. Click **Add->Wire** to add wire or you can use the hot key 'w'. Refer to Figure 7 below to see how the connections are made. Notice that as you get closer to a device or node when placing wire, a small diamond appears. This is where you need to click to place a wire. If you make a mistake click on the error and select **Edit->Delete**.

Once you have completed adding all components and wire, Figure 7, click the "check mark" icon on the left of the window. This will check your work for errors and save your work to the library. The same can be done with **Design->Check and Save**. Any errors will be reported in the CIW.

## V

### SCHOOL OF ENGINEERING

VANDERBILT UNIVERSITY

### EECE 285 – VLSI Design

| <u>v</u>       |                                                                                                                 |         |          |          | Virtu | oso® Sche | ematic | Editing: digi | tal_lil      | b inv s | schema | tic   |         |         |       |        |         |

|----------------|-----------------------------------------------------------------------------------------------------------------|---------|----------|----------|-------|-----------|--------|---------------|--------------|---------|--------|-------|---------|---------|-------|--------|---------|

| Cmd            | test in the second s | Sel:    | 0        |          |       |           |        |               |              |         |        |       |         |         |       |        | 3       |

| Tools          | Design                                                                                                          | Window  | Edit A   | dd Check | Sheet | Options   | NCSU   |               |              |         |        |       |         |         |       |        | Help    |

| V              |                                                                                                                 |         |          |          |       |           |        |               |              | a a     | 5.8    | 2.2   |         |         |       |        | 1       |

|                |                                                                                                                 |         |          |          |       |           |        |               |              |         |        |       |         |         |       |        |         |

| ۲              |                                                                                                                 |         |          |          |       |           |        | · · · ·       |              |         |        |       |         |         |       |        |         |

| € <sup>2</sup> |                                                                                                                 |         |          |          |       |           |        | <b></b> .     |              |         |        |       |         |         |       |        |         |

|                |                                                                                                                 |         |          |          |       |           |        |               |              |         |        |       |         |         |       |        |         |

| R              |                                                                                                                 |         |          |          |       |           |        |               |              |         |        |       |         |         |       |        |         |

| ×              |                                                                                                                 |         |          |          |       |           |        | • •           | -            |         |        |       |         |         |       |        | 5 505   |

| 200            |                                                                                                                 |         |          |          |       |           |        | vdd           |              |         |        |       |         |         |       |        | 86 80 M |

| 2              |                                                                                                                 |         |          |          |       |           |        | in Vddame     | 250          |         |        |       |         |         |       |        | 5 5 C   |

| 1000           |                                                                                                                 |         |          |          |       |           |        | out I=3       | 50.0n<br>30n |         |        |       |         |         |       |        |         |

| 1              |                                                                                                                 |         |          |          |       |           |        | met           |              |         |        |       |         |         |       |        |         |

|                |                                                                                                                 |         |          |          | in    | -         |        |               |              |         | - NOU  |       |         |         |       |        |         |

|                |                                                                                                                 |         |          |          |       |           |        |               |              |         |        |       |         |         |       |        |         |

| ani (          |                                                                                                                 |         |          |          |       |           |        | 1.0           |              |         |        |       |         |         |       |        | 30 60 M |

| 0005           |                                                                                                                 |         |          |          |       |           |        | in NES tarrie | TEAL         |         |        |       |         |         |       |        |         |

| ų              |                                                                                                                 |         |          |          |       |           |        | W=4           | 50.Øn        |         |        |       |         |         |       |        |         |

| -              |                                                                                                                 |         |          |          |       |           |        |               | 32 n         |         |        |       |         |         |       |        |         |

| ۱.۱            |                                                                                                                 |         |          |          |       |           |        |               | _            |         |        |       |         |         |       |        |         |

| r'L            |                                                                                                                 |         |          |          |       |           |        |               |              |         |        |       |         |         |       |        |         |

| _              |                                                                                                                 |         |          |          |       |           |        |               |              |         |        |       |         |         |       |        |         |

| 80C            |                                                                                                                 |         |          |          |       |           |        |               |              |         |        |       |         |         |       |        | 17 25 4 |

|                |                                                                                                                 |         |          |          |       |           |        | e e 💛 e       |              |         |        |       |         |         |       |        | 10.00   |

| •D             |                                                                                                                 |         |          |          |       |           |        |               |              |         |        |       |         |         |       |        |         |

|                |                                                                                                                 |         |          |          |       |           |        |               |              |         |        |       |         |         |       |        |         |

| المتنقا        | 21                                                                                                              |         |          |          |       |           |        |               |              |         |        |       |         |         |       |        |         |

| G              | mouse L                                                                                                         | showCli | ckInfo() | );;;     |       | M: a      | chHiMo | usePopUp()    |              |         | R      | hiDis | playFor | rm ( NC | SU_cr | eateLi | bForm ) |

|                | ×/                                                                                                              |         |          |          |       |           |        |               |              |         |        |       |         |         |       |        |         |

Figure 7: Finished Schematic of the Inverter

4) When the schematic is finished you can print it out. To do this click **Design->Plot->Submit**. The window that appears allows you to select the options for printing, Figure 8. You can print directly from here, or if desired, the schematic can be saved as a file, such as a PostScript. To save to a file click **Plot Options** on the bottom of the window. In the new window, select **Send Plot Only to File** and enter the desired file name, such as plot.ps.

VANDERBILT UNIVERSITY

| A                                                                        | Submit Plot                                                   |                |

|--------------------------------------------------------------------------|---------------------------------------------------------------|----------------|

| OK Cancel D                                                              | efaults Apply                                                 | Help           |

| Plotlibrary                                                              | cellview viewing area                                         |                |

| Library Name                                                             | digital_lib                                                   | Browse         |

| Cell Name                                                                | ing                                                           |                |

| View Name                                                                | schematid                                                     |                |

| Area to Plot                                                             | ((-0.9375 -1.8125) (1.3125 1.5                                | (Full Size)    |

|                                                                          | Full Size Select                                              |                |

| Plot Scope<br>Hierarchy<br>View Name I<br>Skip Uhrarie<br>Skip Cells Be  | s basic sample                                                | down 1         |

| Rotes<br>Template File U<br>Plotter Name def<br>Paper Size A             | <pre>1.2/local/cdssetup/schPlotTempl ault Total Pages 1</pre> | ata Load Save  |

| Plot To File Not                                                         | Selected Plot Options                                         |                |

| OK Cancel I                                                              | Defaults Apply                                                | Help           |

| Plotter Name d<br>Paper Size A                                           | sb<br>lefault<br><br>portrait ~ landscape + automatic         | Image Position |

| Scale 3.1698                                                             | Center Plot 🗍 Fit to Page                                     |                |

|                                                                          | 321 × 10.5000 inches                                          |                |

|                                                                          | 000 × 0.0000                                                  |                |

| Total Plot Size 7.1                                                      | Server ASTA and and a server of                               | Total Pages 1  |

| Number Of Copies<br>J Queue Plot Data<br>Send Plot Only T<br>Mail Log To | Local Tmp Directory /tag<br>At 10 - : 00 - PM -               | Monday _       |

Figure 8: Submit Plot and Plot Options Windows

## **Building a symbol**

This part of the tutorial deals with the layout of the symbolic representation of a circuit, in this case an inverter. As with the schematic, we will create a new cell view for the symbol. You can make the new cell view though any of the methods we have previously discussed. We will also name this view **inv**, but it will be a symbol rather than a schematic, Figure 9.

|          | eate New File | ·                                                   |

|----------|---------------|-----------------------------------------------------|

| Cancel   | Defaults      | Help                                                |

| ame _    | digital_lib   |                                                     |

| , li     | nvį           |                                                     |

| ne 🛛     | yndolį́       |                                                     |

|          | Composer-Syn  | nbol 🔐                                              |

| ath file |               |                                                     |

|          | amei<br>ne    | ame digital_lib<br>ing<br>ne symbol<br>Composer-Sym |

Figure 9: Create New Symbol Window

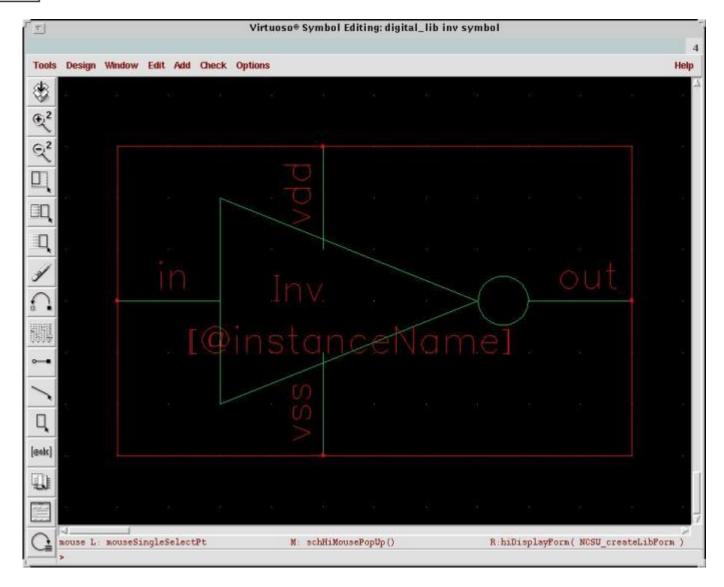

Make sure symbol is the View Name and Composer-Symbol is the Tool. Press OK to continue and a familiar window will appear in which you will draw the symbol, Figure 10.

VANDERBILT UNIVERSITY

Tools Design Window Edit Add Check Options Help ٢ €<sup>2</sup> ି୍ଦ Q Ì £ Q [@abc] C mouse L: mouseSingleSelectPt M: schHiMousePopUp() R: schHiCheckAndSave() 🔁 🛱 🗳 🗇 🚍 ŏ

Figure 10: Virtuoso Symbol Editing Window

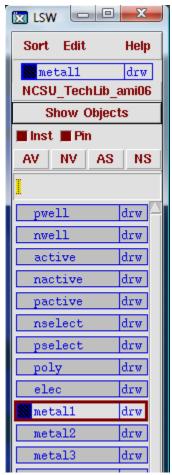

First, we need to draw a triangle on its side to represent the body of the inverter. Draw a vertical line on the left of the center line and connect the ends at a point on the right of center. To access the tools needed to draw the shapes click **Add->Shape->Polygon**. Figure 11 shows this window and other required settings.

Figure 11: Add Shape Window

After adding the triangle, we need to add a circle at the right point to indicate negation. Click **Add->Shape->Circle** and then on the diagram click where you want the center of the circle, move the mouse until the circle is the size you want, and click again to stop sizing the circle.

Next we need to add the pins to our inverter. As before, click **Add->Pin** to bring up the Add Pin Window. We will again create pins **vdd**, **vss**, **in**, and **out**. As in the schematic make sure the pins are specified as **inputOutput**. The Add Pin Window can be seen in figure 12 below.

| A         |        |               | Add Pin          |                     |

|-----------|--------|---------------|------------------|---------------------|

| Hide      | Cancel | Defaults      |                  | Help                |

| Pin Name  | rs     | Judd vas in o | ut               |                     |

| Direction | 0      | inputOutput 🚄 | Bus Expansion 4  | • off 😞 on          |

| Туре      |        | actHi 🚄       | Placement 4      | 🕨 single 😞 multiple |

| Label Of  | fset   |               | Label Location 🔍 | none 🔶 left 😞 right |

| Rotat     | e      |               | Sideways         | Upside Down         |

Figure 12: Add Pin Window

Now we need to place the pins. This is done in the same manner as in the schematic, but these pins are represented differently. On these pins, one end of the line has a small box. This box is the actual pin. Place this box away from the symbol. The shortcut of right click to rotate will save a great bit of time here. Because the pin names may be hard to read now, you can move them by clicking **Edit->Move** or using the shortcut '**m**'.

Now we want to label the symbol. We will add two labels here. Begin by clicking **Add-**>**Label**, which will invoke the Add Label box, Figure 13.

|        | Ad           | d Symbol Labe                                                                                       | el .                                                                                                            |                                                                                                                                         |

|--------|--------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Cancel | Defaults     |                                                                                                     |                                                                                                                 | Help                                                                                                                                    |

| [[     | FinstanceNam | ue ][                                                                                               |                                                                                                                 |                                                                                                                                         |

| ht 0.  | 0625         | Label Choice                                                                                        | instance label                                                                                                  | 1                                                                                                                                       |

| e 📘    | stick 🔟      | Label Type                                                                                          | 🔷 normal Label                                                                                                  |                                                                                                                                         |

| ion lo | werCenter _  | 1                                                                                                   | * NLPLabel                                                                                                      |                                                                                                                                         |

|        | ht 0         | Cancel Defaults       Cancel     Defaults       [@instanceNan       ht     0.0625       e     stick | Cancel Defaults       Cancel Defaults       [@instanceName][       ht     0.0625       e     stick   Label Type | [@instanceName]       ht     0.0625       Label Choice     instance label       e     stick       Stick     Label Type       will shele |

Figure 13: Add Label Window

The first label is going to be the *instance label*. This is the default label as seen above. Place this label near the symbol of the inverter. The second label will be the name label. If the Add Label box disappeared after adding the instance label, bring it back up. Change label type to **normalLabel** and type the name of the device in the Label field, Figure 14. Place this label on or near the symbol. When we place the symbol in schematics, all of the symbols will have the same name, but different instances, e.g. U1, U2, etc.

| 🕅 Add Sy   | mbol Lab | el                    |       |        |                | ×    |

|------------|----------|-----------------------|-------|--------|----------------|------|

| Hide       | Cancel   | Defaults              |       |        |                | Help |

| Label      | I        | ΩV                    | -     |        |                |      |

| Font Heig  | ht 0     | . 0625 <mark>.</mark> | Label | Choice | instance label | -    |

| Font Styl  | e 🗌      | stick =               | Label | Туре   | 🔶 normalLabel  |      |

| Justificat | ion lo   | werCenter             | -     |        | NLPLabel       |      |

|            |          |                       |       |        | ↓ ILLabel      |      |

| Rotate     | e        |                       |       |        |                |      |

Figure 14: Add Symbol Label Window

The last task is to add the selection box to the symbol. Click **Add->Selection Box** and click on the choice of **Automatic** on the window that appears.

The symbol is now finished and should look similar to the symbol below in **Figure 15**. If you are satisfied with the symbol, save it by clicking **Design->Save**.

VANDERBILT UNIVERSITY

### EECE 285 – VLSI Design

Figure 15: The Finished Inverter Symbol

### Simulating the Circuit

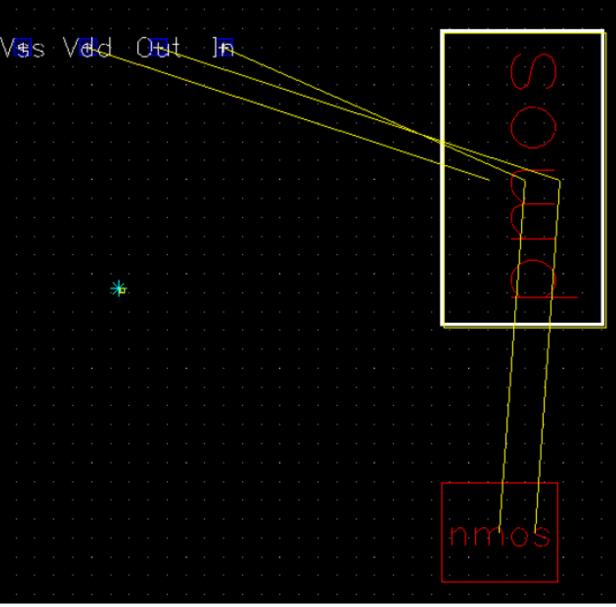

This final part of the tutorial deals with simulating a circuit that has been designed, in this case the inverter. To test out the inverter, we will make a new schematic of a network with the inverter in it. To create a new schematic, we need a new cell view. We can create a new library entirely, but for simplicity, we will create a cell view within our current library. This is done in the same manner in which it was done in all of the previous steps. We will call the new cell view **inv\_test**. Make sure that the selected tool is **Composer-Schematic**.

In the new schematic, we need to add the inverter, two DC voltage supplies, a ground connection, and a capacitor. First we will add the inverter. Click **Add->Instance**, change the library to your library, and select inv. Place it in the center of the schematic. Next we will add the two voltage supplies. The first we will add is the input supply. Click **Add->Instance**, change to NCSU\_Analog\_Parts, click Voltage Supplies, and select vdc, Figure 14. Place the first supply to the left of the **in** pin on the inverter. You may want to rotate the supply so that it is horizontal with the positive terminal closest to the **in** pin. Before placing the next supply (the vdd supply) we need to change a parameter for the supply. In the Add Instance window, set the DC Voltage to 5 V. Place the supply at the top of the schematic.

| S.           |           |          | Add Inst     | ance    |             |

|--------------|-----------|----------|--------------|---------|-------------|

| Hide         | Cancel    | Defaults |              |         | Help        |

| Library 1    | ICSU_An:  | alog_Par | tš           |         | Browse      |

| Cell         | zdoj      |          |              |         |             |

| View         | symboli   |          |              |         |             |

| Names 🏾      |           |          |              |         |             |

| Array        | F         | Rows     | 1            | Columns |             |

| Rotate       |           | Si       | deways       |         | Upside Down |

| AC magnitu   | de        |          | V.           |         |             |

| AC phase     |           |          | Ľ.           |         |             |

| DC voltage   |           |          | 5 ¥ <u>I</u> |         |             |

| Noise file n | ame       |          | ļ.           |         |             |

| Number of    | noise/fre | eq pairs | <u>ď</u>     |         |             |

| _            |           |          | Y            |         |             |

Figure 14: Add instance of 5V DC voltage supply

Next we need to add the ground connection below the **vss** pin of the inverter. This is found under Supply\_Nets in NCSU\_Analog\_Parts. We also need to add a capacitor at the output of the inverter to act as a load. This is found under Parasitic\_Devices in NCSU\_Analog\_Lib. When all of the components are placed, we need to add a pin at the output of the circuit. Add a pin called out. This pin should be an INPUToutput pin as have all of the previous pins. The finished circuit should look similar to the one below:

VANDERBILT UNIVERSITY

### EECE 285 – VLSI Design

| <u>v</u> ] |            |     |     |     |      |         |     |      |     |   |      |     | ٧i       | rtu      | 05 | 0@  | S   | che | em  | at  | tic | Ed  | liti  | ng  | i: n | ny. | _li | ib i | inv | '_t | es | t s | ch | e m   | nat | ic |     |     |     |     |     |    |    |        |   |     |        |     |

|------------|------------|-----|-----|-----|------|---------|-----|------|-----|---|------|-----|----------|----------|----|-----|-----|-----|-----|-----|-----|-----|-------|-----|------|-----|-----|------|-----|-----|----|-----|----|-------|-----|----|-----|-----|-----|-----|-----|----|----|--------|---|-----|--------|-----|

| Cmd        | :          |     |     | Se  | 1: 0 |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| Tools      | Desi       | ign | Win | dov | ,    | Edi     | it  | Ac   | ld  | C | he   | ck  | S        | hee      | et | 0   | pti | ons |     | NC  | csi | J   |       |     |      |     |     |      |     |     |    |     | _  |       |     |    |     |     |     |     |     |    |    |        |   | 100 | H      | elp |

| 7          |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

|            |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

|            |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| 2          |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

|            |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| 2          |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| ×          |            |     |     |     |      |         |     | Γ    |     |   |      |     |          | ł        | -( | 0   | -   | i.  |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

|            |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    | 5=0 |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| ×8×        |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    | PV. |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

|            |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     | 1   |     |     |     | /dd |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| /          |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     | 0   | 1   | 1.    |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| 1000       |            |     |     |     |      |         |     |      |     | ~ |      |     |          |          |    |     |     |     |     |     |     |     |       | 1   |      |     | 8   | 1 80 |     |     |    |     |    |       |     |    | -28 |     |     |     |     |    |    |        |   |     |        |     |

| ]          |            |     |     |     |      |         |     | 1    | -   | U | Nigs | -   |          |          |    |     |     |     |     | NJA |     |     |       |     | ,/   | /   | ×   | 7    |     |     |    |     |    |       |     |    | 2   | 01  | UL. |     |     |    |    |        |   |     |        |     |

|            |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     | X   |       | /   |      |     |     |      |     |     |    |     | C  |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

|            |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     | 10  |       |     |      |     |     |      |     |     |    | 1   |    | c:1p  |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| *hunt      |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     | 3   |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

|            |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| <b>,</b>   |            |     |     |     |      |         |     | -    |     |   |      | -01 |          |          |    |     |     |     | ••• |     |     | 1   | qu    | d   |      |     |     |      | 344 |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| -          |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     | 7   | 7.    |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

|            |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| ត          |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

|            |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

| $\supset$  |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

|            |            |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

|            | 8 S        | 8   | 8 B | 8   | 22   | 93<br>9 | ÷2  | 12   | : 3 | 3 | 2    | £3  | <u> </u> | <u>i</u> | 12 | ŝ   | ŝŝ  |     | \$3 | ŝ   | 32  | 1   | S - S | 8 B | 2    | 2   | ŝ   | ŝ.   | 22  | ŝ   | 1  | 2   |    | \$î - | 33  | 2  | Ş   | 32  | 82  | ŝ   | 1   | 22 | 32 | 22 - T | 2 | 22  | 12 - S |     |

|            | √<br>mouse | L : | sho | wC. | Lic  | kI      | nfo | o () |     | _ | _    | _   | _        |          |    | _   | 3   | M : | 30  | hF  | HiM | lou | seP   | op  | Up   | ()  |     |      |     | _   |    |     |    | R     | : e | ch | Hi  | Dre | at  | eIn | ist | 0  |    |        | _ | _   | 1      | ×   |

|            | >          |     |     |     |      |         |     |      |     |   |      |     |          |          |    |     |     |     |     |     |     |     |       |     |      |     |     |      |     |     |    |     |    |       |     |    |     |     |     |     |     |    |    |        |   |     |        |     |

Figure 15: The test schematic

2) We are now ready to simulate this schematic. Click **Tools->Analog Environment** to open the window that gives access to the simulation tools, Figure 16.

VANDERBILT UNIVERSITY

| r Affir                         | ma Analog Circuit Design Environment (1)   |                     |

|---------------------------------|--------------------------------------------|---------------------|

| Status: Ready                   | T=27 C Simulator: spectr                   | e 4                 |

| Session Setup Analyses          | Variables Outputs Simulation Results Tools | Help                |

| Design                          | Analyses                                   | Ł                   |

| Library my_lib                  | # Type Arguments Enable                    | JAC<br>FTRAN<br>JDC |

| Cell inv_test<br>View schematic |                                            | III<br>III<br>XYZ   |

| Design Variables                | Outputs                                    | Œ,                  |

| # Name Value                    | # Name/Signal/Expr Value Plot Save March   | 4                   |

|                                 |                                            |                     |

|                                 |                                            | 8                   |

| >                               | 1                                          | $\sim$              |

Figure 16: The Analog Environment Window

Make sure the simulator is set to **spectreS**. Go to the tab, Setup, and select Simulator/Directory/Host... In this window make sure that simulator is set to specterS.

| 🗽 Choosi  | ng Simulat | or/Director | y/Host Virtuoso® Analog Design Environment (1) | x    |

|-----------|------------|-------------|------------------------------------------------|------|

| ОК        | Cancel     | Defaults    |                                                | Help |

| Simulator |            | spectr      | eS =                                           |      |

| Project D | irectory   | /nfs/jf     | fs3/users/dickk/cadence/simulation             |      |

| Host Mod  | le         | 🔶 local     | $\Diamond$ remote $ \diamondsuit $ distributed |      |

| Host      |            |             |                                                |      |

| Remote D  | )irectory  |             |                                                |      |

#### Figure 17: Setting up the simulator

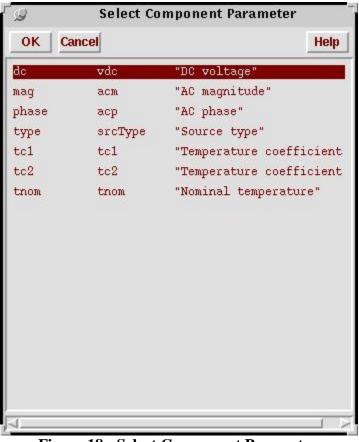

Now we need to specify what we want to do with our simulation. We first need to specify our analysis, click **Analyses->Choose**. In the window that appears, select **dc** and click **Component Parameter**. Next double click **Select Component**, so that you can select the input DC voltage source on the schematic, Figure 18. This will bring up another window in which you need to select the parameter of the source that will be used in the analysis. Select **dc**.

VANDERBILT UNIVERSITY

Figure 18: Select Component Parameter

Next enter the starting and stopping voltages for the supply (Start: 0V, Stop: 5V). Select linear for **Sweep Type** and make the **Step Size** 0.1. The Analysis window should appear similar to the one below:

SCHOOL OF ENGINEERING IVERSITY

EECE 285 – VLSI Design

|     | ZAN  |       |    | ъъ  | <br>т. |     |  |

|-----|------|-------|----|-----|--------|-----|--|

| · · | 10.0 | 4 1.4 | 18 | K 8 | <br>   | JIN |  |

| ок                    | Cancel                           | Defaults       | Apply                                                                     |                                                                             |                         | Help |

|-----------------------|----------------------------------|----------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------|------|

| Analysi               |                                  |                | <ul> <li>◆ dc</li> <li>◆ sens</li> <li>◆ pac</li> <li>◆ pdisto</li> </ul> | <ul> <li>↓ ac</li> <li>↓ sp</li> <li>↓ pnoise</li> <li>↓ qpnoise</li> </ul> |                         |      |

| 0 0                   | c 0                              | rating Poin    | DC Analys                                                                 | is                                                                          |                         |      |

| 💷 De                  | mperat<br>sign Va<br>mpone       | ture           |                                                                           | oonent Name<br>Select Co<br>neter Name                                      | /VQ̃<br>omponent<br>dcš |      |

| ∳ Ce<br>Sweep<br>Line | art-Sti<br>nter-S<br>Type<br>ear | op Sta<br>Ipan | art ( <u>č</u>                                                            | Sto<br>Size<br>er of Steps                                                  | p <u></u> [5<br>]0.1]   |      |

| Add Sp                | ecific I                         | Points 🔟       |                                                                           |                                                                             |                         |      |